# SIDE TE

Under the ouspices of Prof. DIBI Zohir Rector of the University Lorbi Ben M'hidi Dum El Bouaghi, Algeria.

# FORMAL SPECIFICATION OF ON-CHIP COMMUNICATIONS: STATE OF THE ART

Zerdani Amina, Boutekkouk Fateh, Derdouri Lakhdar UNIVERSITY OF LARBI BEN M'HIDI, OUM EL BOUAGHI

#### **ABSTRACT**

Nowadays Systems-on-Chip (SoCs) have evolved considerably in term of performances, reliability and integration capacity that has induced the growth of the number of cores (IPs) in a same chip. In fact, multiplying the core's number of the same chip has conducted to internal signals communication problems and conventional buses were not able to manage too many cores with too many signals. To resolve this problem of intra-communication between the elements of a same chip, a new concept has been introduced which is a direct result of the complexity of recent and future SoCs, it is the Network on Chips(NoC). In this poster we present a state of the art on few formals methods that improve the specification of communication in Network on Chips according to their on-chip communication, the problems they address and the different languages they use.

Keywords— network on chip, formal specification, formal methods, wormhole switching, routing, communication.

# 1. INTRODUCTION

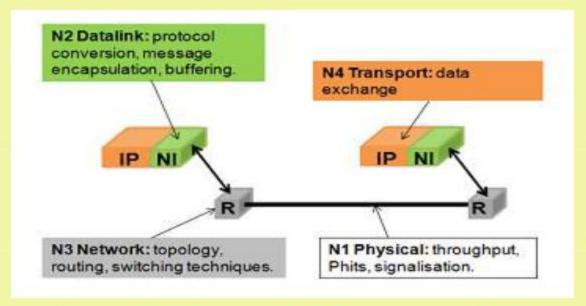

The NoC paradigm has been herald as the solution to the communication limitation that System-On-Chip (SoC) poses [1]. NOC was important because it allowed design engineers to follow technology advancements and so, integrating many cores at the same chip overcoming the intracommunication problems [2]. Generally, NOC are evaluated with respect to performance parameters, such as energy consumption, communication area, bandwidth, throughput and latency [3]. NOC exploits a layered approach to ensure data transfer between IPs, which can processors, memories, dedicated blocks, etc. Figure 1 present the elements of a cummon NOC: Network Interfaces(NI), Physical Links (PL) and Routers (R) [4].

Figure 1. Elements of common NOC.

In this poster, we present a stat of the art on formals methods that improve the specification of communication in Network on

Chips. We introduce some concepts of NOCs and define the communication in NOCs. Next, we present the some works on formal specification of the communication inside NOCs [5].

#### 2. COMMUNICATION IN NOC

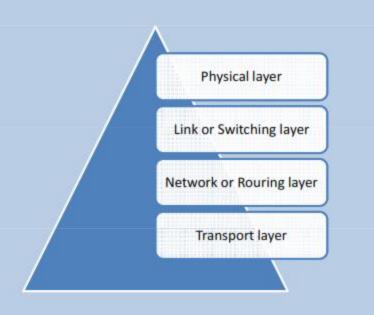

Figure 2. NOC Layers.

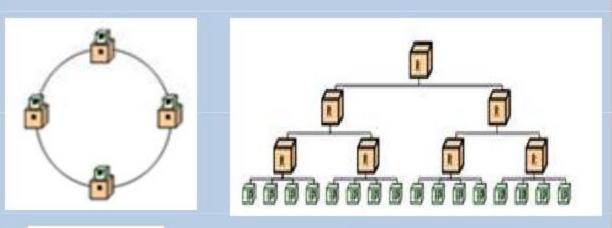

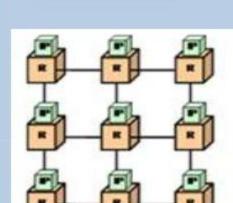

Ring Topology

3D-Topology

Tree Topology

2D-Topology

Figure 3. NOC Topologies.

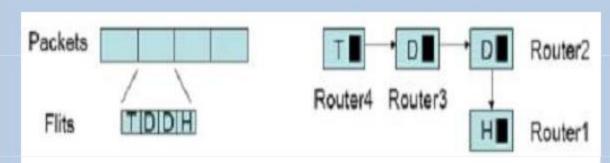

Figure 4. Wormhole Switching.

# 3. FORMAL METHODS

The application domain of SOC spans from home use electronics to large safety critical control and data transfer systems. One of the appropriate approaches for specifying reliable SOC, modeling the on–chip communication, as well as verifying their design is provided by formal methods [6]. The main advantage of formal methods use is the possibility to prove all cases by extending the test space. As formal languages have mathematical foundation, it is possible to formally verify essential design properties [7].

#### 4. RELATED WORKS

Specification of NoC models may be classified based on the specification methodology, as shown in Table 1.

| Reference | Formal Method      | NOC       | Routing Algorithm | Switching         | Success | Failed |

|-----------|--------------------|-----------|-------------------|-------------------|---------|--------|

| [7]       | Z notation         | 2D Mesh   | *:                | -                 | +       | ٠      |

| [8]       | Concurrent Haskell | SpiNNaker | •.                | •                 | +       | *      |

| [9]       | ACL2 Logic         | Octagon   | Shortest Path     | Circuit Switching | +       |        |

| [10]      | ACL2 Sedan         | HERMES    | XY routing        | Wormhole          | +       |        |

| [11]      | SDL                | KTH-VTT   | Dynamic           | •                 | +       | *      |

| [12]      | PVS                | ÆTHEREAL  | *                 | packet switch     | +       | •      |

| [13]      | Promela            | PNOC      |                   | Circuit Switching | +       |        |

Table 1.Comparaison of formal specification methods of NOC.

#### 5.CONCLUSION

Several formal methods for specification and verification of NoC can be found in the literature. By suggestion and comparison of some techniques, the results can help designers to have a more realistic model and a more accurate analysis.

# REFERENCES

- E.O.Attah and M.O. Agyeman, "A Survey of Recent Contributions on Low Power NoC Architectures," in Computing Conference 2017, London, UK, July 2017, pp. 1086-1090.

- A. B. Achballah and S. B. Saoud, "A survey of network-on-chip tools," *International Journal of Advanced Computer Science and Applications (IJACSA)*, vol. 4, no. 9, 2013.

- S.Khan, S.Anjum, U.A.Gulzari, and F.S.Torres, "Comparative analysis of network-on-chip simulation tools," *IET Computers & Digital Techniques*, vol. 12,vol. 1, pp. 30-38, 2018.

- A. B. Achballah and S. B. Saoud, "The design of a network-on-chip architecture based on an avionic protocol," International Journal of Advanced Computer Science and Applications (IJACSA), vol. abs/1401.4891, 2014.

- B.Fateh, "Formal Specification and Verification of Communication in Network-On-Chip: An Overview," International Journal of Recent Contributions from Engineering, Science & IT (iJES), vol. 6, no. 4, pp. 15-31, November 2018.

- L.Tsiopoulos, "Formal Model-Based development of Network-on-Chip systems," PhD.thesis, Åbo Akademi University, Turku, Finland, 2010.

- K. D. N.Ramos, C.M. F. A.Ribeiro, A. M.Moreira, and I.S.Silva, "A Formal approach for Network-On-Chip design," in iiWAS2006: The 8th International Conference on Information Integration and Web-based Application & Services, Yogyakarta Indonesia, December 2006, pp. 347-358.

- D.Lester and D.Richards, "Specification of a network-on-chip," in In Proceedings of the 20th UK Asynchronous Forum (UK-ASYNC), 2008.

J.Schmaltz and D.Borrione, "A Functional Approach to the Formal Specification of

- Networks on Chip," in 5 th Conference Formal Methods in Computer-Aided Design(

FMCAD), Austin,T()exas, USA, 2004, p. 52.66.

- F.Verbeek and J.Schmaltz, "Formal Specification of Networks-on-Chips: Deadlock and Evacuation," in Design, Automation & Test in Europe Conference & Exhibition, Dresden, Germany, 2010.

R.Holsmark, M.Hogberg, and S.Kumar, "Modelling and Evaluation of a Network on Chip

- Architecture using SDL," in Proceedings of 11th International SDL Forum Conference System Design, Stuttgart, Germany, 2003.

12. B.Gebremichael et al., Deadlock Prevention in the ÆTHEREAL Protocol, In CHARME'05

- Proceedings of the 13 IFIP WG 10.5 international conference on Correct Hardware Design and Verification Methods, . Saarbrücken, Germany, 2005,pp. 345-348.

13. A.Zaman and O.Hasan, "Formal verification of circuit-switched Network on chip (NoC)

- architectures using SPIN," in International Symposium on System-on-Chip (SoC),

Tampere, Finland, 2014.

# **Contact Information**

# **Corresponding author's Name**

Address

Tel: +213 6-99116706

Email: amina.zerdani@gmail.com

Fateh boutekkouk@yahoo.fr derdouril@yahoo.fr