**Corrigé type : FPGA et langage de description matérielle (HDL)**

**1<sup>ère</sup> année Master (2025-2026)**

**Exercice 1 (4 pts) :**

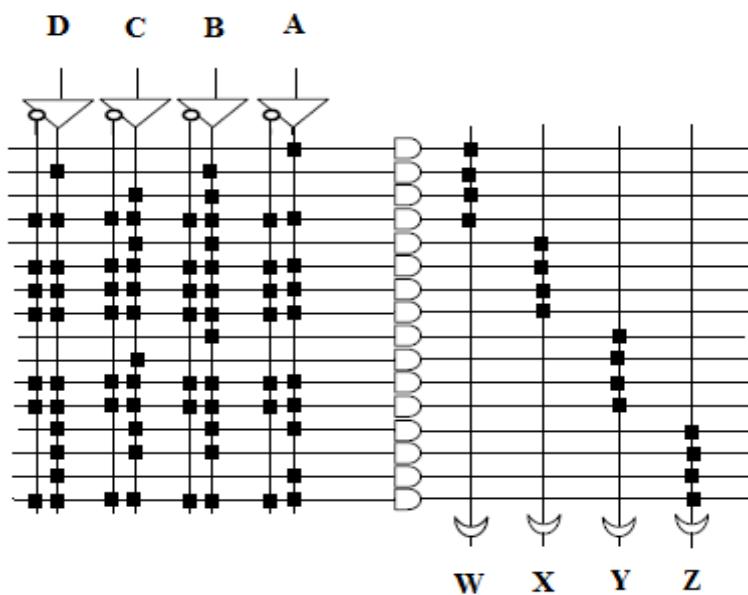

Soit PAL à 4 entrées (A, B, C, D) et 4 sorties (W, X, Y, Z), comme le montre dans la figure ci-dessous :

1) Déduire la formule des fonctions de sorties (W, X, Y, Z)

$$\begin{aligned}

W &= A + B*D + B*C & 0.5 \\

X &= B*C & 0.5 \\

Y &= B + C & 0.5 \\

Z &= A.B.C.D + B.C.D + A.D & 0.5

\end{aligned}$$

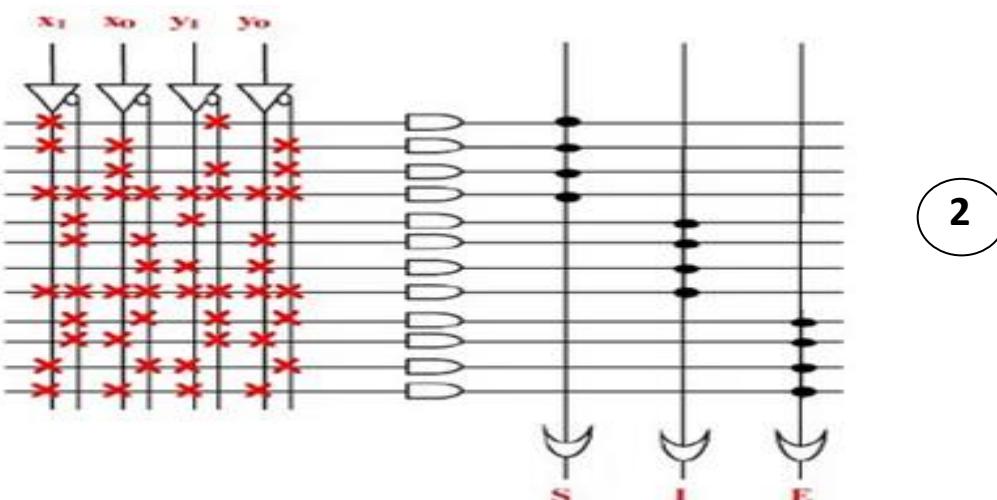

2) Soit Les fonctions :

$$\begin{aligned}

S &= x_1\bar{y}_1 + x_1x_0\bar{y}_0 + x_0\bar{y}_1\bar{y}_0 \\

I &= \bar{x}_1y_1 + \bar{x}_1\bar{x}_0y_0 + \bar{x}_0y_1y_0 \\

E &= \bar{x}_1\bar{x}_0\bar{y}_1\bar{y}_0 + \bar{x}_1x_0\bar{y}_1y_0 + x_1\bar{x}_0y_1\bar{y}_0 + x_1x_0y_1y_0

\end{aligned}$$

Réaliser ces fonctions sur un PAL à 4 entrées et 3 sorties

## Exercice 2 (13 pts)

1) Ecrivez une description en VHDL d'un additionneur complet 1 bit en utilisant l'instruction **component** et **port map**

```

library IEEE;

use IEEE.std_logic_1164.all;

entity fulladd is

port(

a : in STD_LOGIC;

b : in STD_LOGIC;

cin : in STD_LOGIC;

cout : out STD_LOGIC;

s : out STD_LOGIC

);

end fulladd;

architecture full of fulladd is

component halfadd

port (

a : in STD_LOGIC;

b : in STD_LOGIC;

c : out STD_LOGIC;

s : out STD_LOGIC

);

end component;

signal c1 : STD_LOGIC;

signal c2 : STD_LOGIC;

signal s1 : STD_LOGIC;

begin

U1 : halfadd

port map(

a => a, b => b, c => c1, s => s1);

U2 : halfadd

port map(

a => s1, b => cin, c => c2, s => s);

cout <= c2 or c1;

end full;

```

1

1

1

1

1

2) Soit la description VHDL suivante :

```

library IEEE;

use IEEE.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity Exercice2 is

port(A, B: in std_logic;

S1, S2, S3, S4: out std_logic);

end Exercice2;

architecture struct of Exercice2 is

begin

S1<= '1' when (a= '0' and b= '0') else '0';

S2<= '1' when (a= '1' and b= '0') else '0';

S3<= '1' when (a= '0' and b= '1') else '0';

S4<= '1' when (a= '1' and b= '1') else '0';

end struct;

```

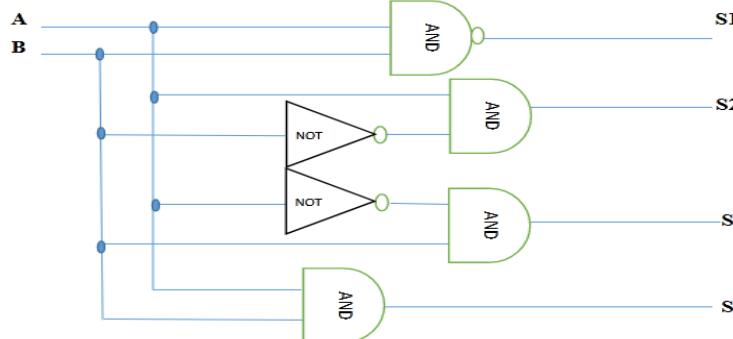

2.1) Déduire de ce programme la table de vérité et le schéma bloc du circuit ?

2.2) De quel circuit s'agit-il ?

2.3) La structure électronique dans cette description est-elle combinatoire ou séquentielle ?

1) Le schéma bloc du circuit

$$S1 = A \cdot B$$

$$S2 = A \cdot \bar{B}$$

$$S3 = \bar{A} \cdot B$$

$$S4 = \bar{A} \cdot \bar{B}$$

1

| B | A | S4 | S3 | S2 | S1 |

|---|---|----|----|----|----|

| 0 | 0 | 0  | 0  | 0  | 1  |

| 0 | 1 | 0  | 0  | 1  | 0  |

| 1 | 0 | 0  | 1  | 0  | 0  |

| 1 | 1 | 1  | 0  | 0  | 0  |

1

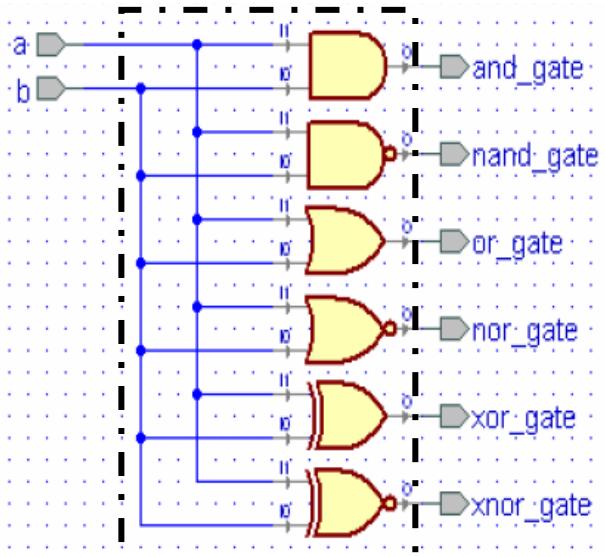

3) Ecrivez une description VHDL à partir du circuit suivant ?

```

library IEEE;

use IEEE.std_logic_1164.all;

entity gates is

port(

a :in STD_LOGIC;

b :in STD_LOGIC;

and_gate :out STD_LOGIC;

nand_gate :out STD_LOGIC;

nor_gate :out STD_LOGIC;

or_gate :out STD_LOGIC;

xnor_gate :out STD_LOGIC;

xor_gate :out STD_LOGIC

);

end gates;

architecture structof gates is

begin

and_gate<= b and a;

nand_gate<= not(b and a);

or_gate<= b or a;

nor_gate<= not(b or a);

xor_gate<= b xor a;

xnor_gate<= not(b xor a);

end struct;

```

2

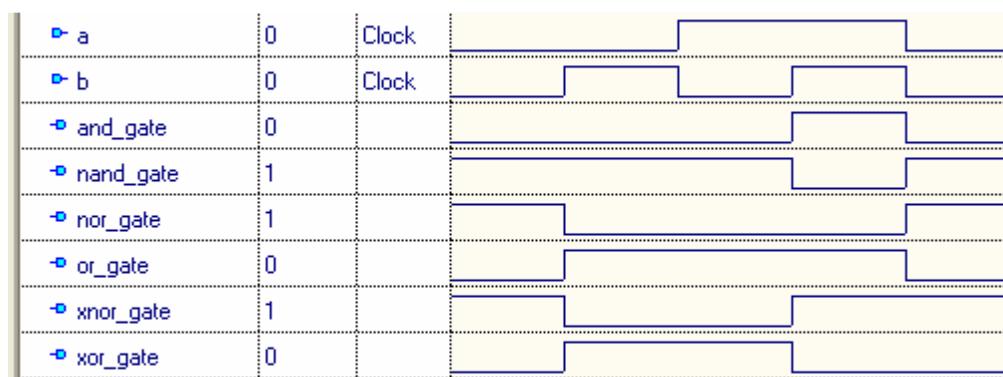

3.1) Donnez le chronogramme des entrées et de sorties concernant ce programme (le respect de l'alternance des états d'entrée pour a et b et obligatoire c.à.d. ab : 00 01 10 11 )

2

### Exercice 3 (3 pts)

1) Un FPGA est composé à la base de :

- Un réseau de CLB

- Un réseau d'interconnexions programmables entre les blocs

- Des blocs d'entrée et de sortie avec le monde extérieur

1.5

2) Indiquez, pour chacune des expressions suivantes, quelle technologie cible lui correspond le mieux dans la liste suivante: FPGA, CPLD, PAL.

- Dispositifs logiques programmables ayant la plus haute densité **CPLD**

- Dispositifs logiques programmables complexes le plus souvent configurables via une mémoire vive statique **FPGA**

- Dispositifs logiques programmables une seule fois **PAL**

0.5

0.5

0.5